# AI-assisted Field Plate Design of GaN HEMT Device

Xiang, Xiaofeng; Palash, Rafid; Yagyu, Eiji; Dunham, Scott; Teo, Koon Hoo; Chowdhury, Nadim

TR2024-152 November 02, 2024

#### Abstract

GaN HEMTs plays a vital role in high-power and high-frequency electronics. Meeting the demanding performance requirements of these devices without compromising reliability is a challenging endeavor. Field Plates are employed to redistribute the electric field, minimizing the risk of device failure, especially in high-voltage operations. While machine learning has been applied to GaN device design, its application to field plate structures, known for their geometric complexity, is limited. This study introduces a novel approach to streamlining the field plate design process. It transforms complex 2D field plate 2 structures into a concise feature space, reducing data requirements. A machine learning- assisted design framework is proposed to optimize field plate structures and perform inverse design. This approach is not exclusive to the design of GaN HEMTs and can be extended to various semiconductor devices with field plate structures. The framework combines technology computer-aided design (TCAD), machine learning, and optimization, streamlining the design process.

Advanced Theory and Simulation 2024

© 2024 MERL. This work may not be copied or reproduced in whole or in part for any commercial purpose. Permission to copy in whole or in part without payment of fee is granted for nonprofit educational and research purposes provided that all such whole or partial copies include the following: a notice that such copying is by permission of Mitsubishi Electric Research Laboratories, Inc.; an acknowledgment of the authors and individual contributions to the work; and all applicable portions of the copyright notice. Copying, reproduction, or republishing for any other purpose shall require a license with payment of fee to Mitsubishi Electric Research Laboratories, Inc. All rights reserved.

Mitsubishi Electric Research Laboratories, Inc. 201 Broadway, Cambridge, Massachusetts 02139

# **AI-assisted Field Plate Design of GaN HEMT Device**

Xiaofeng Xiang, Rafid Hassan Palash, Eiji Yagyu, Scott T. Dunham, Koon Hoo Teo and Nadim Chowdhury

Xiaofeng Xiang Molecular Engineering & Sciences Institute University of Washington Seattle, Washington 98195, USA

Rafid Hassan Palash Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology Dhaka 1205, Bangladesh

Eiji Yagyu Advanced Technology Research and Development Center Mitsubishi Electric Corporation Amagasaki 661-8661, Japan

Scott T. Dunham Department of Electrical and Computer Engineering University of Washington Seattle, Washington 98195, USA

Koon Hoo Teo Mitsubishi Electric Research Laboratories Cambridge, MA 02139

Nadim Chowdhury Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology Dhaka 1205, Bangladesh

Keywords: GaN, Field Plate, Machine Learning, TCAD, Inverse Design

Abstract— GaN HEMTs plays a vital role in high-power and high-frequency electronics. Meeting the demanding performance requirements of these devices without compromising reliability is a challenging endeavor. Field Plates are employed to redistribute the electric field, minimizing the risk of device failure, especially in high-voltage operations. While machine learning has been applied to GaN device design, its application to field plate structures, known for their geometric complexity, is limited. This study introduces a novel approach to streamlining the field plate design process. It transforms complex 2D field plate structures into a concise feature space, reducing data requirements. A machine learningassisted design framework is proposed to optimize field plate structures and perform inverse design. This approach is not exclusive to the design of GaN HEMTs and can be extended to various semiconductor devices with field plate structures. The framework combines technology computer-aided design (TCAD), machine learning, and optimization, streamlining the design process.

## 1. Introduction

GaN High Electron Mobility Transistors (HEMTs) have found extensive use in highpower and high-frequency electronic devices, including chargers,<sup>[1]</sup> RF,<sup>[2,3]</sup> and microwave power applications [4]. Meeting the performance demands of these applications without compromising reliability requires innovative design approaches. Particularly in high-voltage operation, the risk of device failure is concentrated near the gate edge due to the higher electric field. To mitigate this risk, Field Plates are employed to distribute the electric field along the channel, reducing the peak electric field and enhancing device reliability [6-10]. Recent efforts have combined Technology Computer-Aided Design (TCAD) with machine learning and optimization techniques to optimize GaN device design [11-14]. However, most of these endeavors have focused on relatively simple device structures, characterized by a limited set of design parameters. Field plates, on the other hand, exhibit substantial geometric variations that present challenges for applying artificial intelligence (AI) methods in their design. Previous study have demonstrated the optimization of field plates to achieve high breakdown voltage using Artificial Neural Networks [24]. However, these methods have proved less flexible in terms of the field plate structure and have not achieved the desired optimization for other crucial parameters such as gate-drain capacitance and leakage current.

In this study, we present a novel approach for transforming complex field plate structures into a concise feature space, enabling their integration into machine learning models with minimal data requirements. We subsequently propose a machine learning-assisted design framework aimed at optimizing field plate structures to achieve a desired blocking voltage while ensuring reasonable gate-drain capacitance and leakage current. This approach, which includes inverse design, offers a promising solution to address this unique design challenge. This approach is not only effective for GaN HEMTs but also easily transferable to other

transistors featuring field plate structures, such as Si [15-16], SiC [17-19] and GaAs [20-22]. Through appropriate feature engineering, this methodology extends its applicability across a broad range of semiconductor devices. Compared to traditional response surface methodology (RSM) or other design of experiments (DOE) method, this TCAD+AI strategy largely reduces the technology development time and provide more functionalities.

## 2. TCAD Simulation

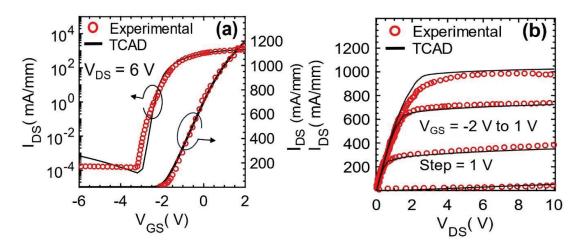

Sentaurus TCAD is used to simulate GaN HEMT device. The TCAD model, provided by Synopsys, has been meticulously calibrated to match experimental data [5]. Specifically, the relationship between carrier saturation velocity  $(v_{sat})$  and sheet charge densities  $(n_{sh})$  has been accurately calibrated against experimental results via high-field saturation model (Caughey-Thomas model). Additionally, trap densities are used to calibrate the carbon profiles in the carbon-doped buffer and channel regions to match experimental data closely (3.30e18 cm<sup>-3</sup> acceptor defect, energy level 0.9 eV from valence band and 1.70e18 cm<sup>-3</sup> donor defect, energy level 0.4 eV from conduction band in buffer region; 5.28e16 cm<sup>-3</sup> acceptor defect, energy level 0.9 eV from valence band and 2.72e16 cm<sup>-3</sup> donor defect, energy level 0.3 eV from conduction band in channel region; 3.8e12 cm<sup>-3</sup> donor defect, energy level from 1.29 eV to 1.45 eV from midgap using uniform distribution, 4.7e12 cm<sup>-3</sup> donor defect, energy level from 1.15 eV to 1.29 eV from midgap using uniform distribution, 2.4e12 cm<sup>-3</sup> donor defect, energy level from 0.99 eV to 1.15 eV from midgap using uniform distribution, 1.4e12 cm<sup>-3</sup> donor defect, energy level from 0.75 eV to 1.99 eV from midgap using uniform distribution at interface of GaN/Nitride). Other parameters, such as subthreshold swing (≈210 mV/decade), drain-induced barrier lowering (DIBL) effects (≈45 mV/V) and the sheet charge densities in these regions are also carefully calibrated ( $\approx 7.4e12 \text{ cm}^{-2}$ ). Furthermore, the relationship between carrier mobility under low electric field conditions and sheet charge densities simulated by the inversion and accumulation layer mobility model (IALMob) has been aligned with experimental observations. Doping-dependent mobility model is also turned on to further improve mobility values. The ID-VGS and ID-VDS curves show good agreement with experimental data (Fig. 1), ensuring the reliability of our simulation model for the GaN HEMT devices studied.

**Figure 1.** Calibration of TCAD simulation models based on experimental data from [5] (a)  $I_{D}$ -V<sub>GS</sub> (b)  $I_{D}$ -V<sub>DS</sub> characteristics. All relevant physics models such as Doping Dependent Mobility, Caughey-Thomas Model, Fermi statistic for carrier density calculation, Thermionic emission for charge injection, SRH Recombination (both hole and electron capture cross sections are set to be 1e-15 cm<sup>2</sup>) and Piezoelectric Polarization (strain activation is 1.0 at barrier/channel, 0.1 at cap layer/barrier and 0.05 at GaN/Nitride) are included [23]. An excellent match is observed.

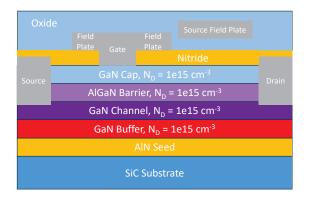

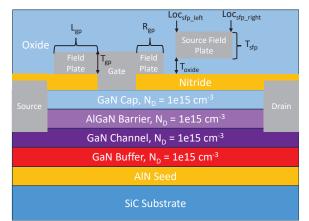

Using the calibrated model parameters for GaN HEMT mentioned before, a typical device structure was developed using Synopsys Sentaurus TCAD tool. The structure is shown in Fig. 2. From bottom to top, the device consists of a SiC substrate, 0.1  $\mu$ m AlN seed layer, 2.0  $\mu$ m GaN buffer layer, 0.05  $\mu$ m GaN channel layer built from epitaxy growth model, 0.02  $\mu$ m AlGaN barrier layer built from epitaxy growth mode, 0.002  $\mu$ m GaN cap layer, 0.1  $\mu$ m Si<sub>3</sub>N<sub>4</sub> nitride layer and 0.2  $\mu$ m oxide layer. Among these layers, channel layer, barrier layer, and cap layer are built from epitaxy growth model. To focus on field plate design, we fix the separation between source and gate to be 1.0  $\mu$ m and separation between gate and drain to be 2.0  $\mu$ m. Lengths of source, gate and drain are fixed to be 0.5  $\mu$ m, 0.35  $\mu$ m and 0.5  $\mu$ m, respectively. Intentional rounding of contact corners during gate formation is employed to facilitate controlled tunneling and achieve a closer resemblance to practical applications.

Figure 2. Schematic of GaN HEMT device structure in TCAD Simulation

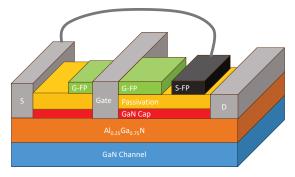

**Figure 3.** A 3D representation of a GaN HEMT device featuring a field plate designed using the method described in this work.

In Fig. 2, Two types of field plate structures are being considered: gate-connected field plate and source-connected field plate. The left side length of gate connected field plate  $L_{gp}$  is fixed to be 0.4 µm as it has a minimal impact on blocking voltage optimization. Conversely, the right-side length of the gate field plate and the thickness of the gate metal are adjustable. Regarding the source field plate structure, the horizontal location, vertical location, and field plate thickness can vary. A 3D representation of our designed GaN HEMT device is shown in Fig. 3.

Three key device performance metrics are extracted from TCAD simulations: off-state blocking voltage (BV), gate-drain capacitance ( $C_{gd}$ ), and gate leakage. We use a standard scheme from [23] to obtain BV. As for  $C_{gd}$ , an AC simulation is conducted at the threshold voltage under zero drain bias with a frequency of 5 GHz. The gate leakage measurement is performed with the device in an off-state and a drain voltage of 24 V. A total of 488 TCAD simulations were generated under these specific settings.

#### 3. Feature Engineering

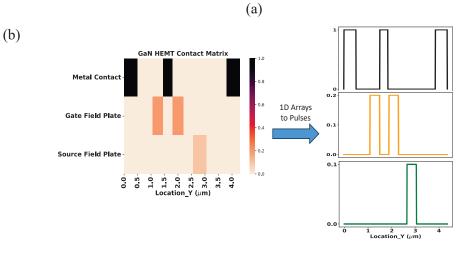

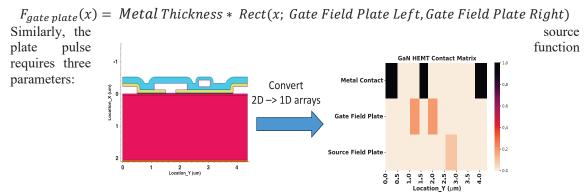

One of the key success factors for machine learning models is feature engineering. The challenge in this work is how to convert field plate structure into features which can be efficiently captured and learned in a ML model. To streamline the analysis, we initially project the 2D field plate structure and metal contact into one-dimensional arrays, as depicted in Fig. 4(a). Each unit within these arrays represents various aspects of the field plate, such as metal plate thickness and oxide thickness above or below it. This transformation results in a 3 x N matrix, where N corresponds to the number of units in each array, based on the chosen resolution. The resolution N was selected based on a balance between computational feasibility and the ability to capture relevant geometrical features of the field plate structures.

For instance, with a transistor width of 4  $\mu$ m and a resolution of 0.05  $\mu$ m, which is sufficient to capture the geometrical features of field plates, each array comprises 80 features. This necessitates a substantial quantity of TCAD runs or experimental data to develop a reliable input to the machine learning model. The geometric aspects of field plates optimized in our study include metal plate thickness of gate and source-connected field plate (parameterized by T<sub>gp</sub> and T<sub>sfp</sub>), oxide thickness below the source connected field plate (parameterized by T<sub>oxide</sub>), length, horizontal and vertical positions of both gate and source connected field plates (parameterized by combination of R<sub>gp</sub>, Loc<sub>sfp</sub> left and Loc<sub>sfp</sub> right).

Figure 4. 2D Field Plate Geometry Transformation Process

To address this data challenge, we implement a second transformation, as depicted in Fig. 4(b). We convert the 1D arrays into a series of pulse functions, which is particularly effective given the sparse nature of the 1D feature array. In the example provided earlier, the metal plate array is transformed into three rectangular pulse functions, each requiring only two parameters (the left and right electrode locations):

### $F_{metal \ plate}(x) = Rect(x; Electrode \ Left, Electrode \ right)$

The gate field plate array is transformed into two rectangular pulse functions, with just three parameters (Metal Thickness, Gate Field Plate Left and Gate Field Plate Right) for each function needed to represent the metal thickness and the field plate's location:

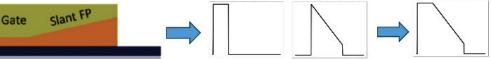

Figure 5. Convert slant field plate into a pulse function via coupling of rectangular and sawtooth pulse functions.

For more intricate field plate structures, such as a slant field plate shown in Fig. 5, we can employ triangular, sawtooth, Gaussian, or other pulse functions to decode the field plate's configuration. This method significantly reduces feature dimensions while retaining sufficient information for effective machine learning. It is important to note that as the complexity of the field plate structures increases, resulting in higher feature dimensions, more data is required to train the neural network surrogate model effectively. In our study, we considered 6 features, in which  $T_{gp}$  ranges from 0.2  $\mu$ m to 0.6  $\mu$ m,  $T_{sfp}$  ranges from 0 to 0.6  $\mu$ m,  $T_{oxide}$ ranges from 0 to 0.2  $\mu$ m, R<sub>gp</sub> ranges from 0.2  $\mu$ m to 1.6  $\mu$ m, Loc<sub>sfp\_left</sub> ranges from 2.35  $\mu$ m to 3.25  $\mu$ m, L<sub>sfp</sub> ranges from 0  $\mu$ m to 1.2  $\mu$ m (Loc<sub>sfp</sub> right = Loc<sub>sfp</sub> left + L<sub>sfp</sub>), and L<sub>gp</sub> is kept at 0.4 μm. Slant field plate is not included. Around 500 TCAD simulations were sufficient to train a well-performing model, which took about a month of CPU time. When the number of features doubles, we anticipate that the required TCAD data will also double to achieve a robust model. However, running TCAD simulations on a computer cluster with multiple CPUs can significantly reduce the training time. While the training time of the neural network surrogate model increases with more data and features, this process takes less than 10 minutes on one GPU for our current model, and the execution time of the neural network model is faster, typically completed in 5 minutes. Therefore, we expect the most time-consuming step to be the TCAD data generation. Thus, while the generation of TCAD data is the most timeconsuming step, the overall process remains manageable. Based on our observations, we estimate that optimizing up to 70-80 metrics with acceptable complexity is feasible in one month if leveraging parallel computing resources (> 8 CPUs) for TCAD data generation.

4. AI-assisted Design Framework

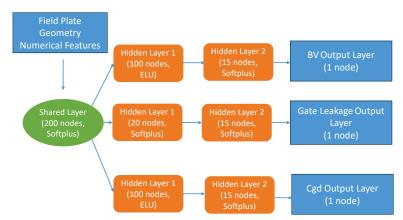

Following the feature transformation, we utilized the TCAD dataset to train a robust neural network surrogate model, the hyperparameter of which is optimized via Bayesian

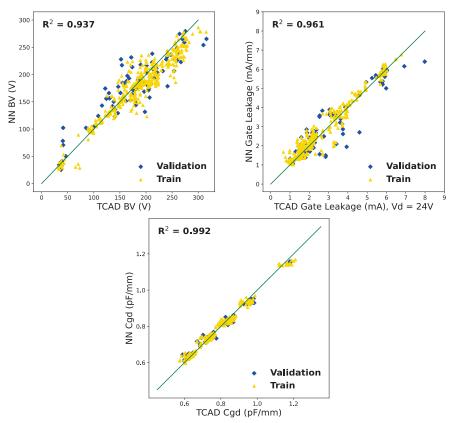

Optimization. The dataset was divided into 80% for training and 20% for validation and testing. Fig. 6 provides an overview of the neural network model's architecture, featuring three output layers, each responsible for predicting one of the performance metrics. The training and validation results are presented in Fig. 7 and Table 1. These results demonstrate the model's capability to well predict key metrics, including BV, C<sub>gd</sub>, and gate leakage except for that the BV prediction in the high BV region is saturated due to the lack of BV data in high BV region. This is also reported in other literature [12].

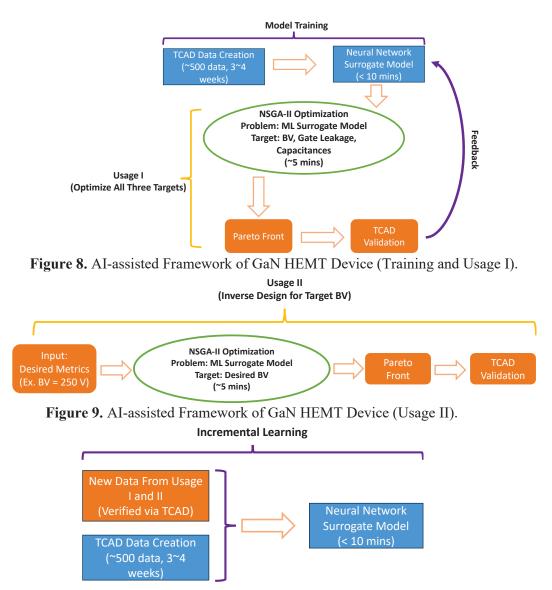

Subsequently, we employ an AI-assisted framework, illustrated in Fig. 8 and Fig. 9, The neural network model is then integrated into the NSGA-II optimization framework as an optimization problem to co-optimize three key performance metrics of GaN HEMT devices: blocking voltage, gate leakage, and capacitance. These three metrics are optimized under the constraints of physical dimension of device structures. Optimizing gate leakage reduces power dissipation, leading to more efficient operation. Reducing C<sub>gd</sub> capacitance increases the speed of operation and further improves efficiency. Additionally, a high BV allows MOSFETs to operate safely in high-voltage environments, which is critical for applications such as power supplies, motor drives, and inverters where high voltages are common. This comprehensive optimization ensures that the MOSFETs deliver enhanced performance across various metrics while maintaining reliability and efficiency. There are two optimization strategies. The first in Fig. 8 aims to optimize all three metrics, which involves maximizing BV while minimizing gate leakage and C<sub>gd</sub>. The second strategy in Fig. 9 targets a specific BV value while minimizing gate leakage and C<sub>gd</sub>. The latter approach is commonly known as inverse design. The algorithm is illustrated in following equations:

$\begin{array}{l} \max f_{BV}(x; \ F_{metal \ plate}, F_{gate \ plate}, F_{source \ plate} \ ) \ \text{or} \\ \min abs(Target \ BV - f_{BV}(x; \ F_{metal \ plate}, F_{gate \ plate}, F_{source \ plate} \ )) \ \text{for inverse design} \\ \min f_{gate\_leakage}(x; \ F_{metal \ plate}, F_{gate \ plate}, F_{source \ plate} \ ) \\ \min f_{C_{gd}}(x; \ F_{metal \ plate}, F_{gate \ plate}, F_{source \ plate} \ ) \\ Subject \ to: \\ Source \ Field \ Plate \ Right < Left \ of \ Drain \\ Source \ Field \ Plate \ Left > \ Gate \ Field \ Plate \ Left \\ Source \ Field \ Plate \ Right - \ Source \ Field \ Plate \ Left \\ Source \ Field \ Plate \ Right - \ Source \ Field \ Plate \ Left > 0 \end{array}$

To further enhance the performance of surrogate model, we will let the surrogate model acquire new information from Usage I and II and do an Incremental Learning (shown in Fig. 10).

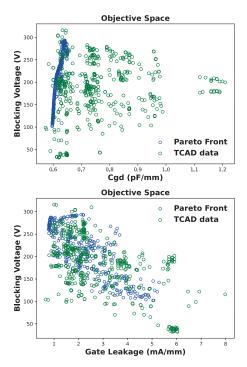

The framework can produce Pareto front points, as demonstrated as blue dots in Fig. 11 and Fig. 12, representing potential optimal solutions. Subsequently, these solutions are subjected to validation via TCAD models. The validation results from TCAD provide

feedback to the system, which allows us to tune the neural network model to the best performance.

Figure 6. Architecture of Neural Network Model.

**Figure. 7** Training (yellow) and validation (blue) parity plots of the NN model. Green lines show ideal predictions where NN Predication is equal to TCAD. The R<sup>2</sup> of the whole dataset is shown on the top left.

|                    | Blocking Voltage<br>(V) | Gate Leakage<br>(mA/mm) | C <sub>gd</sub><br>(pF/mm) |

|--------------------|-------------------------|-------------------------|----------------------------|

| Training<br>RMSE   | 20.83                   | 0.36                    | 1.76e-2                    |

| Validation<br>RMSE | 27.75                   | 0.59                    | 2.10e-2                    |

Table 1. Training and validation RMSE of the NN Model

Figure 10. Incremental Learning of NN Surrogate Model.

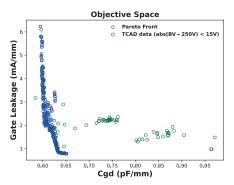

The validation results for both optimization strategies are provided in Tables 2 and 3. These results indicate that we have been able to slightly surpass the maximum BV value in the TCAD dataset (315 V) by 1%, while effectively suppressing gate leakage by up to 23% and reducing capacitance by up to 9%. A schematic and detailed dimensions of device structure for Pareto Front 2 is shown in Fig. 13 and Table 4. It's noteworthy that the predicted BV values in the table are slightly below the maximum BV value from the TCAD data due to insufficient training data at high BV region. This implies that while the surrogate model provides a good approximation, it may not fully capture the extreme values observed in TCAD simulations due to the saturation effect. Nonetheless, it's important to highlight that our approach demonstrates the capability to exceed the maximum BV value present in the TCAD data, suggesting that saturation mentioned in previous discussion in this section and in [12], isn't a significant concern for our optimization process. The surrogate model's predictions are still valuable for guiding the design improvements. In the context of inverse design, we set the target BV value at 250 V and obtained several feasible solutions through this framework. This not only allows us to achieve the target BV value but also optimize gate leakage and capacitance concurrently. Importantly, once a reliable AI framework is established, it significantly reduces model iteration cycles and accelerates technology development compared to traditional methods.

**Figure 11.** Pareto Front generated via AI-assisted model for device optimization. First plot shows BV vs.  $C_{gd}$  and second plot shows BV vs. gate leakage. Blue dots indicate Pareto Front, while green dots indicate TCAD simulation data.

**Figure 12.** Pareto Front for Inverse Design of GaN HEMT with a target blocking voltage 250V (Gate leakage vs.  $C_{gd}$ ). Blue dots indicate Pareto Front, while green dots indicate TCAD simulation data with BV values close to 250V.

| Pareto<br>Front | BV<br>(NN) | Gate<br>Leakage<br>(NN) | C <sub>gd</sub><br>(NN) | BV<br>(TCAD) | Gate<br>Leakage<br>(TCAD) | C <sub>gd</sub><br>(TCAD) |

|-----------------|------------|-------------------------|-------------------------|--------------|---------------------------|---------------------------|

| 1               | 272.65     | 1.57                    | 0.632                   | 316.15       | 1.93                      | 0.609                     |

| 2               | 280.22     | 1.65                    | 0.635                   | 317.75       | 2.35                      | 0.633                     |

| 3               | 273.47     | 2.24                    | 0.635                   | 307.19       | 2.56                      | 0.640                     |

| 4               | 285.09     | 1.49                    | 0.638                   | 303.67       | 1.84                      | 0.620                     |

| 5               | 285.38     | 1.49                    | 0.638                   | 304.63       | 1.52                      | 0.620                     |

| 6               | 284.76     | 1.49                    | 0.639                   | 308.23       | 1.68                      | 0.573                     |

**Table 2.** NN predictions and TCAD validation results of a subset of Pareto Front for BV (V),gate leakage (mA/mm) and Cgd (pF/mm) optimization.

| Pareto<br>Front | Gate<br>Leakage<br>(NN) | C <sub>gd</sub><br>(NN) | BV<br>(TCAD) | Gate<br>Leakage<br>(TCAD) | C <sub>gd</sub><br>(TCAD) |

|-----------------|-------------------------|-------------------------|--------------|---------------------------|---------------------------|

| 1               | 1.77                    | 0.764                   | 267.11       | 1.94                      | 0.765                     |

| 2               | 1.91                    | 0.626                   | 264.31       | 2.96                      | 0.585                     |

| 3               | 1.98                    | 0.625                   | 247.19       | 3.20                      | 0.610                     |

| 4               | 2.22                    | 0.626                   | 254.87       | 3.27                      | 0.620                     |

| 5               | 1.86                    | 0.626                   | 247.83       | 4.66                      | 0.642                     |

**Table 3.** NN prediction and TCAD validations results of a subset of Pareto Front for inversedesign with target BV of 250 V. (We don't include BV results from NN model since thedifference between NN BV and target BV is very small.)

**Figure 13.** 2D Schematic of GaN HEMT device structure of Pareto Front 2 in Table 2, where  $L_{gp}$  denotes left side gate field plate length,  $R_{gp}$  denotes right side gate field plate length,  $T_{gp}$  denotes gate field plate thickness,  $Loc_{sfp\_left}$  denotes horizontal location of left side of source field plate,  $Loc_{sfp\_right}$  denotes horizontal location of right side of source field plate,  $T_{sfp}$  denotes thickness if source field plate and  $T_{oxide}$  denotes oxide layer thickness beneath source field plate.

| <b>Pareto Front</b>      | Value (µm) |  |

|--------------------------|------------|--|

| $L_{gp}$                 | 0.40       |  |

| R <sub>gp</sub>          | 0.20       |  |

| Tgp                      | 0.59       |  |

| Loc <sub>sfp left</sub>  | 2.34       |  |

| Loc <sub>sfp right</sub> | 2.74       |  |

| T <sub>sfp</sub>         | 0.59       |  |

| Toxide                   | 0.13       |  |

Table 4. Dimensions of device structure in Fig. 13.

5. Conclusion

In summary, this work presents a groundbreaking method to optimize semiconductor devices, focusing on GaN HEMTs and their counterparts. By transforming complex field plate structures into a concise feature space and integrating them with machine learning, we have addressed a significant challenge in semiconductor device design. The proposed AI-assisted framework effectively enhances the design and performance of GaN HEMTs, even enabling inverse design capabilities. Both two usages successfully achieve their respective goals, with the first method providing a balanced optimization of all three metrics, and the second method effectively achieving a target BV value while optimizing the other two metrics. Moreover, the approach is versatile and can be applied to other transistors featuring field plate structures, making it a valuable tool for a broad range of semiconductor devices. This work represents a promising step forward in semiconductor device design, offering efficiency and reliability to meet the demands of high-power and high-frequency electronic applications.

#### References

[1] Lu, J., Liu, G., Bai, H., Brown, A., Johnson, P.M., McAmmond, M. and Taylor, A.R, *IEEE Transactions on Transportation Electrification*, **2017**, 3(3), pp. 554-564.

Micovic, M., Brown, D.F., Regan, D., Wong, J., Tang, Y., Herrault, F., Santos, D.,

Burnham, S.D., Tai, J., Prophet, E. and Khalaf, I., presented at *IEEE International Electron Devices Meeting (IEDM)*, December, 2016.

[3] Hoo Teo, K., Zhang, Y., Chowdhury, N., Rakheja, S., Ma, R., Xie, Q., Yagyu, E.,

Yamanaka, K., Li, K. and Palacios, T., *Journal of Applied Physics*, 2021, 130(16).

[4] Binari, S.C., Ikossi, K., Roussos, J.A., Kruppa, W., Park, D., Dietrich, H.B., Koleske,

D.D., Wickenden, A.E. and Henry, R.L., *IEEE Transactions on Electron Devices*, 2001,

48(3), pp. 465-471..

[5] faile

[6] Bothe, K.M., Ganguly, S., Guo, J., Liu, Y., Niyonzima, A., Tornblad, O., Fisher, J., Gajewski, D.A., Sheppard, S.T. and Noori, B., *IEEE Electron Device Letters*, **2022**, 43(3), pp.354-357.

[7] Xu, T., Tang, Z., Zhou, Z. and Zhou, B., *Micromachines*, **2023**, 14(6), p. 1121.

[8] Chanchal, C., Visvkarma, A.K., Malik, A., Laishram, R., Rawal, D.S. and Saxena, M., presented at *IEEE VLSI Device Circuit and System (VLSI DCS)*, February, **2022**.

[9] Bai, Z., Chai, S., Zhao, C. and Wang, L., *Journal of Electronic Materials*, 2023, 52(6), pp.3892-3902.

[10] Wang, P., Mi, M., Chen, Y.L., An, S., Zhou, Y., Zhou, J., Zhao, Z., Zhu, Q., Du, X.,Gong, C. and Li, M., *Semiconductor Science and Technology*, 2023.

[11] Wang, Z., Li, L. and Yao, Y., *IEEE Transactions on Electron Devices*, 2021, 68(5),

pp. 2212-2219.

[12] Yee, N., Lu, A., Wang, Y., Porter, M., Zhang, Y. and Wong, H.Y., presented at 35th *International Symposium on Power Semiconductor Devices and ICs (ISPSD)*, May **2023**.

[13] Mehta, K., Raju, S.S., Xiao, M., Wang, B., Zhang, Y. and Wong, H.Y., *IEEE Access*,2020, 8, pp. 143519-143529.

[14] Lu, A., Marshall, J., Wang, Y., Xiao, M., Zhang, Y. and Wong, H.Y., *Solid-State Electronics*, **2022**, 198, p.108468.

[15] Conti, F. and Conti, M., Solid-State Electronics, 1972, 15(1), pp.93-105.

[16] Jaume, D., Charitat, G., Reynes, J.M. and Rossel, P., *IEEE Transactions on Electron Devices*, **1991**, 38(7), pp.1681-1684.

[17] Yu, H., Wang, J., Liang, S., Deng, G., Liu, H., Ji, B. and Shen, Z.J., *IET Power Electronics*, **2022**, 15(14), pp.1502-1510.

[18] Mohammad, S.N., Kub, F.J. and Eddy, C.R., *Journal of Vacuum Science & Technology B*, **2011**, 29(2).

[19] Nilsson, P.Å., Allerstam, F., Sudow, M., Andersson, K., Hjelmgren, H.,

Sveinbjornsson, E.Ö. and Rorsman, N., *IEEE transactions on electron devices*, **2008**, 55(8), pp.1875-1879.

- [20] Hori, Y., Kuzuhara, M., Ando, Y. and Mizuta, M., *Journal of Applied Physics*, 2000, 87(7), pp.3483-3487.

- [21] Horio, K., Tanaka, T., Itagaki, K. and Nakajima, A., *IEEE transactions on electron devices*, **2010**, 58(3), pp.698-703.

- [22] Chiu, H.C. and Cheng, C.S., *IEEE electron device letters*, **2010**, 31(3), pp.186-188.

- [23] Synopsys, Inc. Sentaurus<sup>TM</sup> Device User Guide Version V-2023.12, CA, USA, 2023.

- [24] Liu, S., Duan, X., Wang, S., Zhang, J. and Hao, Y., *IEEE Transactions on Device and Materials Reliability*, vol. 23, no. 2, pp. 204-210